# EMPIRICAL EVALUATION OF A QUEUEING NETWORK MODEL FOR SEMICONDUCTOR WAFER FABRICATION

# HONG CHEN, J. MICHAEL HARRISON, AVI MANDELBAUM, ANN VAN ACKERE, and LAWRENCE M. WEIN

Stanford University, Stanford, California (Received December 1986; revision received May 1987; accepted October 1987)

This paper concerns performance modeling of semiconductor manufacturing operations. More specifically, it focuses on queueing network models for an analysis of wafer fabrication facilities. The congestion problems that plague wafer fabrication facilities are described in general terms, and several years' operating data from one particular facility are summarized. A simple queueing network model of that facility is constructed, and the model is used to predict certain key system performance measures. The values predicted by the model are found to be within about 10% of those actually observed. These results suggest that queueing network models can provide useful quantitative guidance to designers of wafer fabrication facilities, and we discuss refinements and extensions of our elementary model that are likely to be important in other settings. However, an even more important benefit to be gained from queueing theory is the simple qualitative point that congestion and delay in wafer fabrication are caused by variability in the operating environment. To significantly reduce manufacturing cycle times, one must reduce that variability.

his paper is concerned with rough-cut performance modeling of semiconductor manufacturing operations. Attention is restricted to the wafer fabrication stage of integrated circuit (IC) production, and the performance measures of primary interest are the average throughput rate and manufacturing cycle time. We describe a modeling study and a data analysis aimed at empirical validation of the model constructed, hoping to build confidence in analytical queueing models, as opposed to simulation studies, and thus pave the way for their use in applied work. This introductory section contains a brief and highly selective description of IC manufacturing, an account of the congestion problems that plague wafer fabrication, an overview of performance modeling, and an outline of the remainder of the paper.

An integrated circuit, commonly referred to as an IC or a semiconductor chip, is a complex device that consists of miniaturized electronic components and their interconnections. The production of IC's is accomplished in a four-stage process that begins with raw wafers of silicon or, less commonly, gallium arsenide. Wafers are grouped in *lots*, the members of which travel together in a standard container and are destined for conversion to the same final product. The lot size, usually between 20 and 100 wafers, differs from one production facility to another and may differ from one product to another within the same facility.

The first stage of IC production is called wafer

processing or wafer fabrication. It is conducted in a so-called clean room, where special means are employed to maintain a low density of airborne particles. The term wafer fab is commonly used to mean a clean room in which wafer fabrication is conducted. Here the intricate miniature circuitry for a number of identical chips is created on each wafer. The individual chips-to-be are referred to as dice. The circuitry is created by a lengthy and complex process (described later), and the number of dice per wafer may vary from just a few to many hundreds. Wafer fabrication requires a long sequence of processing steps and involves many separate pieces of equipment, through which lots of wafers are routed in the traditional job shop fashion.

In the second stage of IC production, commonly referred to as wafer probe, the following occurs: (a) the individual dice on a wafer are tested for functionality by delicate electrical probes, (b) dice that fail to meet specifications are marked with an ink dot, (c) the wafers are scored and broken into separate individual dice, and (d) the defective dice are discarded. In the third stage of production, called assembly, electrical leads are connected to the individual dice, which are then encapsulated in plastic or ceramic shells called *packages*. In the fourth stage of production, packaged chips are subjected to a final functional test and burn-in.

Perhaps the greatest single determinant of economic

Subject classification: 683 queueing applications, 697 queueing networks.

success for an IC manufacturer is the total process yield, that is, the fraction of individual dice that survives all stages of production and testing to emerge as salable packaged chips. Total yield may be 80% or higher for relatively simple circuits produced with mature technologies, but figures below 10% are not uncommon for large, highly integrated products in the early stages of production.

The wafer fabrication stage dominates the economics of IC production, and it is here that semiconductor manufacturers concentrate their research and development efforts: wafer fabrication is probably the most complex manufacturing process in the world today, and it requires an enormous investment in plant and equipment. Because capital costs are high and variable processing costs are relatively low, high utilization of wafer fabrication equipment is a generally accepted goal in the semiconductor industry. Most wafer fabs are operated on a three-shift basis for either 5 or 7 days per week, but the amount of time spent to actually process wafers is limited by several factors, such as preventive maintenance, setup, absence of qualified operators, end of shift effects (see Section 2), and frequent episodes of unscheduled downtime. Some of this unscheduled downtime is due to the literal failure of equipment, but "process tuning" is often a more important downtime category. If a manufacturer reduces any of these sources of equipment unavailability, or the time required for actually processing wafers on any given piece of equipment, a higher throughput rate, and hence, a lower unit cost can be achieved, provided that process yields are not adversely affected.

For purposes of this paper, a piece of equipment is idle if it is available for processing but is starved for work. Equivalently, the equipment is idle if it is neither processing wafers nor rendered unavailable for one of the reasons enumerated above. The idleness rate for a piece of equipment is defined as the overall fraction of working hours that it spends in the idle condition. The conventional wisdom among semiconductor manufacturers is that the idleness rate for critical fabrication equipment should be no larger than 10%. Given this, it will come as no surprise to readers familiar with queueing theory that wafers spend most of their time waiting rather than being processed. To set terminology, let us define the cycle time for a lot of wafers as the total number of working hours that elapse between its entry into the clean room and its exit. This same quantity will occasionally be called the manufacturing cycle time or manufacturing interval for wafer fabrication.

To get a feel for the magnitude of queueing effects in IC manufacturing, let us consider a wafer fab dedicated to production of a single, reasonably complicated product (say, a VLSI microprocessor). Production of these circuits involves a total of perhaps 200 distinct fabrication steps, many minor in character. If we add the times required for all of these operations, taking reasonable account of such overhead factors as loading, unloading and operator orientation time, the total might come to 120 hours, which amounts to 1 working week with three-shift operations 5 days per week. Under such circumstances, the average throughput time for wafer fabrication would typically be 5-10 weeks. In the semiconductor industry it is common to describe this state of affairs by saying that the actual-to-theoretical ratio is between 5 and 10, or that the manufacturing interval is 5-10 times the theoretical.

The total manufacturing interval for VLSI circuits. considering all stages of production, may be as long as 4 months, and this is widely recognized as a major problem for semiconductor manufacturers. In the case of customized products, the nature of the problem is obvious, since the order lead-time imposed on customers must be at least as large as the total manufacturing interval. On the other hand, standardized products can be made to stock, but here again, long manufacturing intervals cause trouble because production must be based on forecasts of market demand many months in the future, and major demand shifts are commonplace. Moreover, product life cycles are short in the semiconductor industry, so the risk of obsolescence for finished goods inventory is always present. Finally, there is an established negative correlation between manufacturing interval and yield in wafer fabrication, which provides another strong motivation for reduction of throughput times.

Thus, it is essential that the designer of a wafer fabrication line has a means to predict key performance measures, including average throughput time, given only processing system characteristics that are known or can reasonably be estimated before the system goes into operation. The most obvious means to generate such performance predictors is the Monte Carlo simulation, but experience in other areas suggests that mathematically tractable queueing network models, although less flexible than simulation models and based on apparently restrictive assumptions, are far easier to use, generate more qualitative insight with respect to essential system relationships, and are accurate enough to provide quantitative guidance to system designers. Thus, we shall focus our attention

on such models. The potential role of queueing network models for the analysis of manufacturing systems has been recognized before, most notably in the influential paper of Solberg (1977), but such models are not incorporated, thus far, in accepted engineering practice.

Solberg (1983) also noted the general lack of sophistication in manufacturing system design, and his remarks apply even more forcefully to the semiconductor industry, where manufacturing systems engineering is still in its infancy. Nonetheless, there are recent signs of interest in performance modeling of wafer fabrication. Dayhoff and Atherton (1984, 1986a, b, 1987) describe the potential relevance of simulation methodology for analysis of wafer fab operations, and successful wafer fab simulation studies are reported by Spence and Welter (1987) and Burman et al. (1986). The last paper surveys and summarizes the experience of an operations research team involved in the analysis of AT&T wafer fab operations, and discusses queueing network models of the type under consideration here.

The term "system design" has been used frequently in this introduction, and for many readers those words may conjure up a picture of engineers laying out a new physical facility. However, most wafer fab design activity is actually aimed at reconfiguration of existing facilities. Such reconfigurations may occur several times yearly, so rough-cut design tools of the type discussed here have enormous potential value.

The description of wafer fabrication given earlier was implicitly oriented toward production facilities. Research and development laboratories (hereafter referred to as R&D labs or facilities) constitute a second, closely related class of wafer fabs. Wafer processing in such facilities is aimed at the development of new products or processes, as opposed to the production of salable chips, but the equipment, operating procedures, and process flow are essentially the same as in a production facility. In this paper, a particular wafer fab will be analyzed in some detail. It happens to be an R&D lab, but we believe that the differences between R&D facilities and production facilities are relatively unimportant for performance modeling purposes. That is, the same model structure applies in both cases, although the parameter values that characterize the fab may be quite different. This issue will be discussed further in Section 2.

Section 1 describes both the general character of IC wafer fabrication and the particular wafer fab facility alluded to above. In Section 2 we lay out an apparently naive queueing network model of the fab, and the performance predictions of that model are compared

against actual observed performance. For the particular fab facility that we studied, a simple queueing model predicts aggregate performance characteristics with surprising accuracy, but there are several refinements or generalizations of the model that are likely to be important in other settings. Those extensions are discussed in Section 3, along with other potential directions for future research.

### 1. Wafer Processing and the TRC Silicon Fab

This section contains some general information about the operations involved in wafer fabrication, plus specific information about the one wafer fab facility we studied in detail. Readers are referred to Sze (1983) or Gise and Blanchard (1986) for a detailed description of semiconductor wafer fabrication. As stated earlier, wafer fabrication is done in a clean room, which is typically divided into U-shaped bays. A bay generally contains a major piece of equipment on which a basic operation is performed, plus ancillary equipment or facilities involved in closely related operations. Operators process lots on the inside of the U, and most equipment is positioned so that maintenance can be performed on the outside of the U, which is outside the clean room.

Each lot entering the clean room has an associated process flow, often called a recipe, that consists of precisely specified *operations* executed in a prescribed sequence on prescribed pieces of equipment. If all goes well, this exact sequence of operations is performed, but sometimes inspections reveal that an operation was not executed to specification, in which case, some or all of the wafers in the lot are either scrapped or reworked. This latter phenomenon introduces a stochastic element to the routing of lots. Integrated circuit fabrication involves the creation of multiple layers on a silicon wafer, and the operations involved in the creation of each successive layer are essentially the same, so lots can, and typically do, return repeatedly to some pieces of equipment.

### 1.1 Equipment Categories and Major Processing Steps

The wafer fab we studied in detail is the Hewlett-Packard Technology Research Center Silicon Fab (hereafter referred to as the TRC fab), which is a relatively large R&D facility in Palo Alto, California. The TRC fab contains 52 processing centers, which are listed and described in Table I. (The official TRC equipment list is substantially longer than this, but the equipment listed in Table I accounts for all but a small fraction of total queueing and processing time.)

Table I TRC Processing Equipment

| MCLN         Deposition         Clear bench at sputter         LPCLN         Deposition         Clean bench for LPCVD tubes           SLSP         Deposition         Sloan sputter         TU73         Deposition         Low pressure CVD tube           SPUT         Deposition         Plasma enhanced CVD lower tube         TU74         Deposition         Low pressure SI02 CVD tube           PLM5U         Deposition         Plasma enhanced CVD upper tube         TU84         Deposition         ASM-LTO-UPCVD system           PLM5U         Deposition         Plasma enhanced CVD upper tube         PHSOG*         Deposition         Trilayer bottom and spin on glass           CLEAN         Deposition         Clean wet bench for OXI/DIFF tubes         PHPPS*         Lithography         Pre-bake/peative spin resist           TU11         Deposition         Metal alloy tube         PHGCA*         Lithography         Pre-bake/positive spin resist           TU11         Deposition         Field oxidation tube         PHPED*         Lithography         Pre-bake/positive spin resist           TU21         Deposition         Field oxidation tube         PHPED*         Lithography         Two Perkin-Elmer align/developers           TU21         Deposition         P predeposition         PHHB         Lithography         Hardbake statio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Name of<br>Equipment | Operation  | Description               | Name of<br>Equipment | Operation    | Description                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------|---------------------------|----------------------|--------------|-------------------------------|

| Percent   Perc   | MCLN                 | Deposition | Clear bench at sputter    | LPCLN                | Deposition   | Clean bench for LPCVD tubes   |

| PLM5L         Deposition<br>tube         Plasma enhanced CVD lower<br>tube         TU74<br>TU84         Deposition<br>Deposition         Low pressure Sl02 CVD tube<br>ASM-LTO-UPCVD system           PLM5U         Deposition         Plasma enhanced CVD upper<br>tube         PHSOG*         Deposition         Trilayer bottom and spin on<br>glass           CLEAN         Deposition         Clean wet bench for<br>OXI/DIFF tubes         PHPNS<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SLSP                 | Deposition | Sloan sputter             | TU72                 | Deposition   | Low pressure CVD tube         |

| PLM5U Deposition Plasma enhanced CVD upper tube  CLEAN Deposition Clean wet bench for OXI/DIFF tubes PHPPS* Lithography Pre-bake/negative spin resist OXI/DIFF tubes PHPPS* Lithography Pre-bake/negative spin resist TU11 Deposition Field oxidation tube PHPED* Lithography Two GCA align/developers TU24 Deposition Field oxidation tube PHBI Lithography Hardbake station MOS tube PHBI Lithography Hardbake station Bake to personate the public oxidation tube PHFI Lithography Final inspect PHBI Lithography Final inspect PHBI Lithography Final inspect PLM3 Deposition Source drain doping tube PLM4 Etching Plasma reactor-therm "RIE" TU32 Deposition Source drain doping tube PLM4 Etching Plasma etcher for aluminum TU41 Deposition N-well drive-in tube PLM6 Etching Plasma etcher for aluminum TU41 Deposition N-well drive-in tube PLM8 Etching Plasma etcher for aluminum TU42 Deposition N-well drive-in tube PLM2 Etching Plasma II reactor TU43 Deposition Annealing for silicides PLM22 Etching Plasma II etch TU44 Deposition P-well drive-in tube PHWET Etching Plasma II etch TU44 Deposition MOS gate oxidation tube PHPED Etching Plasma II etch TU51 Deposition MOS gate oxidation tube PHPED Etching Plasma II etch TU52 Deposition MOS gate oxidation tube PHPED Etching Plasma II etch TU53 Deposition MOS gate oxidation tube PHPED Etching Plasma II etch TU54 Deposition MOS gate oxidation tube PHPED Etching Plasma II etch TU54 Deposition MOS gate oxidation tube PHCEN Photoresist Strip/clean for plasma etch TU54 Deposition Field oxidation tube IMP1 Ion Old ion implanter Implantation TU64 Deposition Field oxidation tube IMP1 Ion New ion implanter implantation TU64 Deposition Field oxidation tube IMP2 Ion New ion implanter implantation TU64 Deposition Field oxidation tube IMP2 Ion implantation  | SPUT                 | Deposition | Perkin-Elmer 4400 sputter | TU73                 | Deposition   | Low pressure SINI CVD tube    |

| PLM5U Deposition tube  CLEAN Deposition Clean wet bench for DAT/DIFF tubes PHPPS' Lithography Pre-bake/negative spin resist PHPPS' Lithography Pre-bake/negative spin resist PHPPS' Lithography Pre-bake/negative spin resist Lithography Pre-bake/positive spin resist PHPPS' Lithography Pre-bake/positive spin resist Lithography Pre-bake/positive spin resist PHPED' Lithography Pre-bake/positive spin resist Lithography Pre-bake/positive spin resist Lithography Pre-bake/positive spin resist Lithography PHPED' Lithography PHPED' Lithography PHPED' Lithography PHPED' Lithography Developers PHPED Develop inspect PHPED Develop inspect PHPED Lithography PHPED Develop inspect PHPED Lithography PHPED Develop inspect PHPED Lithography PHPED Develop inspect PHPED Develop inspect PHPED Lithography PHPED Develop inspect P | PLM5L                | Deposition | Plasma enhanced CVD lower | TU74                 | Deposition   | Low pressure SI02 CVD tube    |

| tube  CLEAN Deposition Clean wet bench for OXI/DIFF tubes OXI/DIFF tubes DYHPPS' Lithography Pre-bake/positive spin resist TU11 Deposition Metal alloy tube PHGCA' Lithography Two GCA align/developers TU31 Deposition Field oxidation tube PHPD' Lithography Two GCA align/developers TU21 Deposition Field oxidation tube PHPED' Lithography Two Perkin-Elmer align/developers Deposition P predeposition PHBI Lithography Develop inspect Hardbake station MOS tube PHBI Lithography Hardbake station Bake inspect PHBI Lithography Bake inspect Final inspect PLM3 Deposition Source drain doping tube PLM3 Etching Plasma reactor-therm "RIE" AME 8100 PLM4 Deposition Field oxidation tube PLM6 Etching Plasma etcher for aluminum TU41 Deposition N-well drive-in tube PLM8 Etching Plasma etcher for aluminum TU41 Deposition N-well drive-in tube PLM2 Etching Plasma II reactor TU43 Deposition P-well drive-in tube PLM2 Etching Plasma II reactor TU44 Deposition P-well drive-in tube PHWET Etching Wet etch station TU51 Deposition MOS gate oxidation tube PHPLO Etching/ Etchers and strip/clean for TU52 Deposition MOS gate oxidation tube PHCN PhOtoresist Strip/clean for plasma etch TU54 Deposition Field oxidation tube IMP1 Ion Old ion implanter TU61 Deposition Field oxidation tube IMP1 Ion New ion implanter Implantation TU63 Deposition Field oxidation tube IMP1 Ion New ion implanter implantation Im |                      | -          | tube                      | TU84                 | Deposition   | ASM-LTO-UPCVD system          |

| OXI/DIFF tubes  OXI/DIFF tubes  PHPPSb  Lithography  Pre-bake/positive spin resist  TU11  Deposition  Field oxidation tube  TU21  Deposition  Field oxidation tube  PHDI  Lithography  Two GCA align/developers  Tu21  Deposition  Pield oxidation tube  Tu24  Deposition  P predeposition  P predeposition  P predeposition  NoS tube  PHBI  Lithography  PHBI  Lithography  PHBI  Lithography  Bake inspect  Tu31  Deposition  Punce drain doping tube  PLM3  Deposition  PLM3  Deposition  Field oxidation tube  PLM4  Deposition  Field oxidation tube  PLM6  Etching  Plasma reactor-therm "RIE"  Tu34  Deposition  Tu34  Deposition  Field oxidation tube  PLM6  Etching  Plasma etcher for aluminum  Tu41  Deposition  N-well drive-in tube  PLM21  Etching  Plasma II reactor  Tu43  Deposition  Tu44  Deposition  P-well drive-in tube  PLM21  Etching  Plasma II etch  Tu44  Deposition  Tu44  Deposition  P-well drive-in tube  PHWET  Tu51  Deposition  MOS gate oxidation tube  PHVET  Tu52  Deposition  MOS gate oxidation tube  Tu53  Deposition  MOS gate oxidation tube  Tu54  Deposition  MOS gate oxidation tube  Tu54  Deposition  Tu55  Deposition  Field oxidation tube  Tu54  Deposition  Tu64  Deposition  Field oxidation tube  Tu66  Deposition  Field oxidation tube  Tu66  Deposition  Field oxidation tube  Tu67  Deposition  Field oxidation tube  Tu68  Deposition  Field oxidation tube  Tu69  Deposition  Field oxidation tube  Tu60  Deposition  Field oxidation tub | PLM5U                | Deposition | * -                       | PHSOG <sup>a</sup>   | Deposition   | •                             |

| TU11 Deposition Field oxidation tube PHGCA' Lithography Two GCA align/developers TU13 Deposition Field oxidation tube PHPED' Lithography Two Perkin-Elmer align/developers Deposition Field oxidation tube Introduced Physical Physi | CLEAN                | Deposition | Clean wet bench for       | PHPNS                | Lithography  | Pre-bake/negative spin resist |

| TU13 Deposition Field oxidation tube PHPEDd Lithography Two Perkin-Elmer align/developers  TU24 Deposition P predeposition PHDI Lithography Develop inspect  Deposition P predeposition PHHB Lithography Hardbake station  MOS tube PHBI Lithography Hardbake station  MOS tube PHBI Lithography Final inspect  TU31 Deposition Source drain doping tube PLM3 Etching Plasma reactor-therm "RIE"  TU33 Deposition Source drain doping tube PLM4 Etching AME 8100  TU34 Deposition Field oxidation tube PLM6 Etching Plasma etcher for aluminum  TU41 Deposition N-well drive-in tube PLM8 Etching Dxide/nitride dry TEK etch  TU42 Deposition N-well drive-in tube PLM2 Etching Plasma II reactor  TU43 Deposition P-well drive-in tube PLM22 Etching Plasma II etch  TU44 Deposition P-well drive-in tube PHWET Etching Wet etch station  TU51 Deposition MOS gate oxidation tube PHPLO Etching/ Etchers and strip/clean for resist strip plasma etch  TU53 Deposition MOS gate oxidation tube PHCLN Photoresist Strip/clean for wet etch  TU54 Deposition Field oxidation tube IMP1 Ion Old ion implanter  TU61 Deposition Field oxidation tube IMP1 Ion New ion implanter  TU62 Deposition Field oxidation tube implantation  TU63 Deposition Field oxidation tube IMP2 Ion New ion implanter  TU64 Deposition Field oxidation tube implantation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |            | OXI/DIFF tubes            | $PHPPS^b$            | Lithography  | Pre-bake/positive spin resist |

| TU21 Deposition TU24 Deposition P predeposition bipolar/ MOS tube PHBI Deposition PHFI Deposition PHBI Deposit | TU11                 | Deposition | Metal alloy tube          | $PHGCA^c$            | Lithography  | Two GCA align/developers      |

| TU24 Deposition P predeposition bipolar/ PHHB Lithography Hardbake station bipolar/ PHHB Lithography Hardbake station MOS tube PHBI Lithography Bake inspect  TU31 Deposition Special tube PHFI Lithography Final inspect  TU32 Deposition Source drain doping tube PLM3 Etching Plasma reactor-therm "RIE"  TU33 Deposition Source drain doping tube PLM4 Etching AME 8100  TU34 Deposition Field oxidation tube PLM8 Etching Plasma etcher for aluminum TU41 Deposition N-well drive-in tube PLM8 Etching Oxide/nitride dry TEK etch  TU42 Deposition N-well drive-in tube PLM21 Etching Plasma II reactor  TU43 Deposition Annealing for silicides PLM22 Etching Plasma II etch  TU44 Deposition P-well drive-in tube PHWET Etching Wet etch station  TU51 Deposition MOS gate oxidation tube PHPLO Etching/ Etchers and strip/clean for resist strip plasma etch  TU53 Deposition MOS gate oxidation tube PHCLN Photoresist Strip/clean for plasma etch  TU54 Deposition Field oxidation tube IMP1 Ion Old ion implanter  TU61 Deposition Field oxidation tube implantation  TU62 Deposition Field oxidation tube IMP2 Ion New ion implanter  TU64 Deposition Field oxidation tube implantation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TU13                 | Deposition | Field oxidation tube      | $PHPED^d$            | Lithography  | Two Perkin-Elmer              |

| bipolar/ MOS tube PHBI Lithography Bake inspect  TU31 Deposition Special tube PHFI Lithography Final inspect  TU32 Deposition Source drain doping tube PLM3 Etching Plasma reactor-therm "RIE"  TU33 Deposition Source drain doping tube PLM4 Etching AME 8100  TU34 Deposition Field oxidation tube PLM6 Etching Plasma etcher for aluminum  TU41 Deposition N-well drive-in tube PLM8 Etching Plasma II reactor  TU42 Deposition N-well drive-in tube PLM21 Etching Plasma II reactor  TU44 Deposition P-well drive-in tube PHWET Etching Plasma II etch  TU44 Deposition MOS gate oxidation tube PHPLO Etching TU51 Deposition MOS gate oxidation tube TU52 Deposition MOS gate oxidation tube TU53 Deposition MOS gate oxidation tube TU54 Deposition MOS gate oxidation tube TU55 Deposition MOS gate oxidation tube TU54 Deposition Field oxidation tube TU55 Deposition Field oxidation tube TU61 Deposition Field oxidation tube TU62 Deposition Field oxidation tube TU63 Deposition Field oxidation tube TU64 Deposition Field oxidation tube TU65 Deposition Field oxidation tube TU66 TU66 Deposition Field oxidation tube TU67 Deposition Field oxidation tube TU68 Deposition Field oxidation tube TU69 Deposition Field oxidation tube TU60 Deposition Field oxid | TU21                 | Deposition | Field oxidation tube      |                      |              | align/developers              |

| TU31 Deposition Special tube PHFI Lithography Final inspect TU32 Deposition Source drain doping tube PLM3 Etching Plasma reactor-therm "RIE" TU33 Deposition Source drain doping tube PLM4 Etching AME 8100 TU34 Deposition Field oxidation tube PLM6 Etching Plasma etcher for aluminum TU41 Deposition N-well drive-in tube PLM8 Etching Oxide/nitride dry TEK etch TU42 Deposition N-well drive-in tube PLM21 Etching Plasma II reactor TU43 Deposition Annealing for silicides PLM22 Etching Plasma II etch TU44 Deposition P-well drive-in tube PHWET Etching Wet etch station TU51 Deposition MOS gate oxidation tube PHPLO Etching/ Etchers and strip/clean for TU52 Deposition MOS gate oxidation tube TU53 Deposition MOS gate oxidation tube TU54 Deposition MOS gate oxidation tube TU55 Deposition Field oxidation tube TU61 Deposition Field oxidation tube TU62 Deposition Field oxidation tube TU63 Deposition Field oxidation tube TU64 Deposition Field oxidation tube TU65 Deposition Field oxidation tube TU66 Deposition Field oxidation tube TU67 Deposition Field oxidation tube TU68 Deposition Field oxidation tube TU69 Deposition Field oxidation tube                                                                                                                                                                                                                                                     | TU24                 | Deposition | P predeposition           | PHDI                 | Lithography  | Develop inspect               |

| TU31 Deposition Special tube PHFI Lithography Final inspect TU32 Deposition Source drain doping tube PLM3 Etching Plasma reactor-therm "RIE" TU33 Deposition Source drain doping tube PLM4 Etching AME 8100 TU34 Deposition Field oxidation tube PLM6 Etching Plasma etcher for aluminum TU41 Deposition N-well drive-in tube PLM8 Etching Oxide/nitride dry TEK etch TU42 Deposition N-well drive-in tube PLM21 Etching Plasma II reactor TU43 Deposition Annealing for silicides PLM22 Etching Plasma II etch TU44 Deposition P-well drive-in tube PHWET Etching Wet etch station TU51 Deposition MOS gate oxidation tube PHPLO Etching/ Etchers and strip/clean for TU52 Deposition MOS gate oxidation tube PHCLN Photoresist Strip/clean for wet etch TU53 Deposition MOS gate oxidation tube Strip TU61 Deposition Field oxidation tube IMP1 Ion Old ion implanter TU62 Deposition Field oxidation tube IMP1 Ion New ion implanter TU63 Deposition Field oxidation tube IMP2 Ion New ion implanter TU64 Deposition Field oxidation tube implantation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |            | bipolar/                  | PHHB                 | Lithography  | Hardbake station              |

| TU32 Deposition Source drain doping tube PLM3 Etching Plasma reactor-therm "RIE" TU33 Deposition Source drain doping tube PLM4 Etching AME 8100 TU34 Deposition Field oxidation tube PLM6 Etching Plasma etcher for aluminum TU41 Deposition N-well drive-in tube PLM8 Etching Oxide/nitride dry TEK etch TU42 Deposition N-well drive-in tube PLM21 Etching Plasma II reactor TU43 Deposition Annealing for silicides PLM22 Etching Plasma II etch TU44 Deposition P-well drive-in tube PHWET Etching Wet etch station TU51 Deposition MOS gate oxidation tube PHPLO Etching/ Etchers and strip/clean for TU52 Deposition MOS gate oxidation tube PHCLN Photoresist Strip/clean for wet etch TU53 Deposition MOS gate oxidation tube Strip TU61 Deposition Field oxidation tube IMP1 Ion Old ion implanter TU62 Deposition Field oxidation tube IMP2 Ion New ion implanter TU63 Deposition Field oxidation tube implantation TU64 Deposition Field oxidation tube IMP2 Ion New ion implanter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |            | MOS tube                  | PHBI                 | Lithography  | Bake inspect                  |

| TU33 Deposition Source drain doping tube TU34 Deposition Field oxidation tube PLM6 Etching Plasma etcher for aluminum TU41 Deposition N-well drive-in tube PLM8 Etching Oxide/nitride dry TEK etch TU42 Deposition N-well drive-in tube PLM21 Etching Plasma II reactor PLM3 Deposition Annealing for silicides PLM22 Etching Plasma II etch TU44 Deposition P-well drive-in tube PHWET Etching Wet etch station TU51 Deposition MOS gate oxidation tube PHPLO Etching/ Etchers and strip/clean for TU52 Deposition MOS gate oxidation tube TU53 Deposition MOS gate oxidation tube TU54 Deposition MOS gate oxidation tube TU55 Deposition Field oxidation tube TU56 Deposition Field oxidation tube TU61 Deposition Field oxidation tube TU62 Deposition Field oxidation tube TU63 Deposition Field oxidation tube TU64 Deposition Field oxidation tube TU65 Deposition Field oxidation tube TU66 Deposition Field oxidation tube TU67 Deposition Field oxidation tube TU68 Deposition Field oxidation tube TU69 Deposition Field oxidation tube TU60 Deposition Field oxidation tube TU61 Deposition Field oxidation tube TU62 Deposition Field oxidation tube TU63 Deposition Field oxidation tube TU64 Deposition Field oxidation tube TU65 Deposition Field oxidation tube TU66 Deposition Field oxidation tube TU67 Deposition Field oxidation tube TU68 Deposition Field oxidation tube TU69 Deposition Field oxidation tube TU60 Deposition Field oxidation tube TU61 Deposition Field oxidation tube TU62 Deposition Field oxidation tube TU63 Deposition Field oxidation tube TU64 Deposition Field oxidation tube                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TU31                 | Deposition | Special tube              | PHFI                 | Lithography  | Final inspect                 |

| TU34 Deposition Field oxidation tube PLM6 Etching Oxide/nitride dry TEK etch TU41 Deposition N-well drive-in tube PLM8 Etching Oxide/nitride dry TEK etch TU42 Deposition N-well drive-in tube PLM21 Etching Plasma II reactor TU43 Deposition Annealing for silicides PLM22 Etching Plasma II etch TU44 Deposition P-well drive-in tube PHWET Etching Wet etch station TU51 Deposition MOS gate oxidation tube PHPLO Etching/ Etchers and strip/clean for TU52 Deposition MOS gate oxidation tube PHCLN Photoresist Strip/clean for wet etch TU53 Deposition MOS gate oxidation tube PHCLN Photoresist Strip/clean for wet etch TU54 Deposition Field oxidation tube IMP1 Ion Old ion implanter TU61 Deposition Field oxidation tube IMP1 Ion New ion implanter TU63 Deposition Field oxidation tube IMP2 Ion New ion implanter TU64 Deposition Field oxidation tube implantation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TU32                 | Deposition | Source drain doping tube  | PLM3                 | Etching      | Plasma reactor-therm "RIE"    |

| TU41 Deposition N-well drive-in tube PLM8 Etching Oxide/nitride dry TEK etch TU42 Deposition N-well drive-in tube PLM21 Etching Plasma II reactor TU43 Deposition Annealing for silicides PLM22 Etching Plasma II etch TU44 Deposition P-well drive-in tube PHWET Etching Wet etch station TU51 Deposition MOS gate oxidation tube PHPLO Etching/ Etchers and strip/clean for TU52 Deposition MOS gate oxidation tube PHCLN Photoresist Strip/clean for wet etch TU53 Deposition MOS gate oxidation tube PHCLN Photoresist Strip/clean for wet etch TU54 Deposition MOS gate oxidation tube IMP1 Ion Old ion implanter TU61 Deposition Field oxidation tube IMP1 Ion New ion implanter TU63 Deposition Field oxidation tube IMP2 Ion New ion implanter TU64 Deposition Field oxidation tube implantation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TU33                 |            | Source drain doping tube  | PLM4                 | U            |                               |

| TU42 Deposition N-well drive-in tube PLM21 Etching Plasma II reactor TU43 Deposition Annealing for silicides PLM22 Etching Plasma II etch TU44 Deposition P-well drive-in tube PHWET Etching Wet etch station TU51 Deposition MOS gate oxidation tube PHPLO Etching/ Etchers and strip/clean for TU52 Deposition MOS gate oxidation tube resist strip plasma etch TU53 Deposition MOS gate oxidation tube PHCLN Photoresist Strip/clean for wet etch TU54 Deposition MOS gate oxidation tube strip TU61 Deposition Field oxidation tube IMP1 Ion Old ion implanter TU62 Deposition Field oxidation tube IMP2 Ion New ion implanter TU63 Deposition Field oxidation tube implantation TU64 Deposition Field oxidation tube implantation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TU34                 | Deposition | Field oxidation tube      | PLM6                 | Etching      | Plasma etcher for aluminum    |

| TU43 Deposition Annealing for silicides TU44 Deposition P-well drive-in tube PHWET Etching Wet etch station TU51 Deposition MOS gate oxidation tube PHPLO Etching/ Etchers and strip/clean for TU52 Deposition MOS gate oxidation tube resist strip plasma etch TU53 Deposition MOS gate oxidation tube PHCLN Photoresist Strip/clean for wet etch TU54 Deposition MOS gate oxidation tube strip TU61 Deposition Field oxidation tube IMP1 Ion Old ion implanter TU62 Deposition Field oxidation tube IMP2 Ion New ion implanter TU63 Deposition Field oxidation tube implantation TU64 Deposition Field oxidation tube implantation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TU41                 | Deposition | N-well drive-in tube      | PLM8                 | Etching      |                               |

| TU44 Deposition P-well drive-in tube PHWET Etching Wet etch station TU51 Deposition MOS gate oxidation tube PHPLO Etching/ Etchers and strip/clean for TU52 Deposition MOS gate oxidation tube resist strip plasma etch TU53 Deposition MOS gate oxidation tube PHCLN Photoresist Strip/clean for wet etch TU54 Deposition MOS gate oxidation tube strip TU61 Deposition Field oxidation tube IMP1 Ion Old ion implanter TU62 Deposition Field oxidation tube IMP2 Ion New ion implanter TU63 Deposition Field oxidation tube implantation TU64 Deposition Field oxidation tube implantation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TU42                 | Deposition | N-well drive-in tube      | PLM21                | Etching      | Plasma II reactor             |

| TU51 Deposition MOS gate oxidation tube PHPLO Etching/ Etchers and strip/clean for resist strip plasma etch TU52 Deposition MOS gate oxidation tube PHCLN Photoresist Strip/clean for wet etch TU53 Deposition MOS gate oxidation tube Strip TU54 Deposition MOS gate oxidation tube Strip TU61 Deposition Field oxidation tube IMP1 Ion Old ion implanter TU62 Deposition Field oxidation tube IMP2 Ion New ion implanter TU63 Deposition Field oxidation tube implantation TU64 Deposition Field oxidation tube implantation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TU43                 | Deposition | Annealing for silicides   | PLM22                | Etching      | Plasma II etch                |

| TU52 Deposition MOS gate oxidation tube TU53 Deposition MOS gate oxidation tube TU54 Deposition MOS gate oxidation tube TU61 Deposition Field oxidation tube TU62 Deposition Field oxidation tube TU63 Deposition Field oxidation tube TU64 Deposition Field oxidation tube TU65 Deposition Field oxidation tube TU66 Deposition Field oxidation tube TU67 Deposition Field oxidation tube TU68 Deposition Field oxidation tube TU69 Deposition Field oxidation tube                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TU44                 | Deposition | P-well drive-in tube      | PHWET                | Etching      | Wet etch station              |

| TU53 Deposition MOS gate oxidation tube PHCLN Photoresist Strip/clean for wet etch TU54 Deposition MOS gate oxidation tube strip TU61 Deposition Field oxidation tube IMP1 Ion Old ion implanter TU62 Deposition Field oxidation tube implantation TU63 Deposition Field oxidation tube IMP2 Ion New ion implanter TU64 Deposition Field oxidation tube implantation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TU51                 | Deposition | MOS gate oxidation tube   | PHPLO                | Etching/     | Etchers and strip/clean for   |

| TU54 Deposition MOS gate oxidation tube strip TU61 Deposition Field oxidation tube IMP1 Ion Old ion implanter TU62 Deposition Field oxidation tube implantation TU63 Deposition Field oxidation tube IMP2 Ion New ion implanter TU64 Deposition Field oxidation tube implantation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TU52                 | Deposition | MOS gate oxidation tube   |                      | resist strip | plasma etch                   |

| TU61 Deposition Field oxidation tube IMP1 Ion Old ion implanter TU62 Deposition Field oxidation tube implantation TU63 Deposition Field oxidation tube IMP2 Ion New ion implanter TU64 Deposition Field oxidation tube implantation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TU53                 | Deposition |                           | PHCLN                | Photoresist  | Strip/clean for wet etch      |

| TU62 Deposition Field oxidation tube implantation TU63 Deposition Field oxidation tube IMP2 Ion New ion implanter TU64 Deposition Field oxidation tube implantation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TU54                 | Deposition | MOS gate oxidation tube   |                      | strip        |                               |

| TU63 Deposition Field oxidation tube IMP2 Ion New ion implanter TU64 Deposition Field oxidation tube implantation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TU61                 | Deposition | Field oxidation tube      | IMP1                 | Ion          | Old ion implanter             |

| TU64 Deposition Field oxidation tube implantation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TU62                 | Deposition | Field oxidation tube      |                      | implantation |                               |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TU63                 | Deposition | Field oxidation tube      | IMP2                 | Ion          | New ion implanter             |

| TU71 Deposition Alloy tube                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TU64                 | Deposition | Field oxidation tube      |                      | implantation |                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TU71                 | Deposition | Alloy tube                |                      |              |                               |

<sup>&</sup>lt;sup>a</sup> "PHSOG" includes three equipments: "SOG1," "SOG2" and "SOG3."

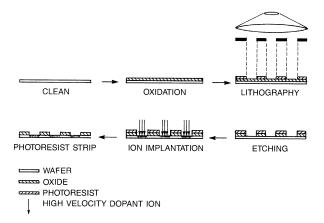

As noted in the table, four of those centers contain several identical pieces of equipment, and for reasons that will be explained later (see Subsection 1.3), each piece of equipment will be treated as a separate service station in our queueing network model of the fab. Individual pieces of equipment will be referred to as stations or machines in the remainder of this paper. Each piece of equipment is associated with one of the five generic operations described in the following paragraphs. In creating any single layer of an integrated circuit, these five operations, or perhaps some subset of them, are executed in the order listed below. Figure 1 gives a pictorial representation of the operations required to create a single layer, and readers may find it helpful to reference this figure when reading the descriptions.

**Deposition.** A thin film of material is deposited to form a layer of the integrated circuit. The wafers must be cleaned immediately before this operation (that is, within a specified time before the operation is performed) to avoid particle contamination. The deposition technologies used by TRC are: (1) oxidation, (2) chemical vapor deposition (CVD), (3) spin on glass (SOG), and (4) physical vapor deposition (sputtering). The TRC fab has one sputtering bay, two CVD bays and six oxidation bays.

Lithography. Also called photolithography, masking or patterning. The wafer is coated with a light-sensitive material called photoresist, which is then exposed to ultraviolet light through a mask that contains a pattern reflecting the intended geometry of the circuit. The

<sup>&</sup>lt;sup>b</sup> "PHPPS" includes two equipments: "POS SPIN1" and "POS SPIN2."

<sup>&</sup>lt;sup>c</sup> "PHGCA" includes two equipments: "GCA1" and "GCA2."

d "PHPED" includes two equipments: "PE1" and "PE2."

**Figure 1.** Illustrative process sequence for fabrication of a single oxide layer.